# IOWA STATE UNIVERSITY Digital Repository

Retrospective Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

1991

## Design of an ISDN central office, U-interface

Timothy N. Toillion *Iowa State University*

Follow this and additional works at: https://lib.dr.iastate.edu/rtd

Part of the <u>Digital Circuits Commons</u>, <u>Digital Communications and Networking Commons</u>, and the <u>Signal Processing Commons</u>

#### Recommended Citation

Toillion, Timothy N., "Design of an ISDN central office, U-interface" (1991). Retrospective Theses and Dissertations. 16968. https://lib.dr.iastate.edu/rtd/16968

This Thesis is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

## Design of an ISDN central office, U-interface

by

Timothy N. Toillion

A Thesis Submitted to the

Graduate Faculty in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

Department: Electrical Engineering and Computer Engineering

Major: Computer Engineering

Signatures have been redacted for privacy

Signatures have been redacted for privacy

Iowa State University Ames, Iowa 1991

Copyright © Timothy N. Toillion, 1991. All rights reserved.

## TABLE OF CONTENTS

| INTRODUCTION                                   | 1  |

|------------------------------------------------|----|

| CHAPTER 1. THE EVOLUTION OF TELECOMMUNICATIONS | 4  |

| Telephone Communications                       | 4  |

| Inventions Spawn Growth                        | 4  |

| Modern Telecommunication Networks              | 8  |

| Telecommunications                             | 11 |

| Definition of Telecommunication                | 11 |

| Other Forms of Telecommunication               | 11 |

| Integration of Services                        | 12 |

| Evolution of the Concept                       | 12 |

| The Evolution of ISDN                          | 15 |

| CCITT's Standards                              | 15 |

| Major Setback                                  | 16 |

| Evolution of Products and Services             | 16 |

| CHAPTER 2. ISDN                                | 18 |

| Services                                       | 18 |

| Functional Architecture                        | 20 |

| Standards                                      | 22 |

|    | CCITT I-Series Recommendations                         | 22       |

|----|--------------------------------------------------------|----------|

|    | ISDN Reference Model                                   | 23       |

|    | The Physical Layer                                     | 25       |

|    | Specified Functions                                    | 25       |

|    | Transmission Rates                                     | 26       |

|    | User-Interface Rates                                   | 26       |

|    | Reference Point Signaling Standards                    | 28       |

|    | The Data Link Layer                                    | 30       |

|    | LAP-D: The D Channel Interface                         | 31       |

|    | LAP-B: The B Channel Interface                         | 32       |

|    | The Network Layer                                      | 33       |

| C. | HAPTER 3. THE ORIGINAL CENTRAL OFFICE DESIGN           | 35       |

|    | Goals                                                  | 35       |

|    | The PC Card                                            | 36       |

|    | The MITEL ST-BUS                                       | 38       |

|    | ST-BUS Timing Generation                               | 39       |

|    | The PC Bus Interface                                   | 41       |

|    | The Primary Rate Interface                             | 42       |

|    | The MT8980D Digital Crosspoint Switch                  | 43       |

|    | The U-Interface Components                             | 47       |

|    | MITEL's MT8972B Digital Network Interface Circuit      |          |

|    | MITEL S MITOSTED DISNAT INCOME INVESTIGACE CITED VICE. | 49       |

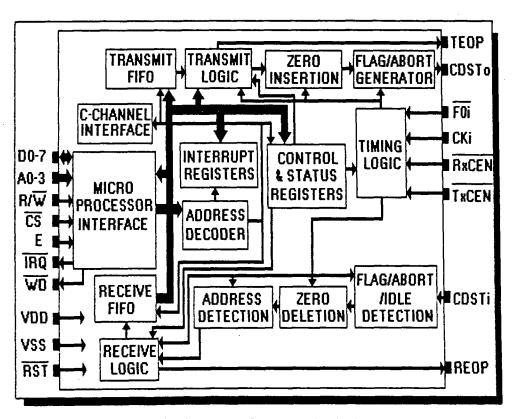

|    | The HDLC Protocol Controller: MT8952                   | 49<br>54 |

|    | •                                                      |          |

| CHAPTER 4. THE REVISED DESIGN OF THE CENTRAL OF-  |    |

|---------------------------------------------------|----|

| FICE                                              | 67 |

| Project Goals                                     | 67 |

| Revised Goals                                     | 67 |

| Added Goals                                       | 68 |

| Division of the Design Project                    | 68 |

| Typical Operation of a Central Office             | 69 |

| Possible Connections                              | 69 |

| Interactions                                      | 70 |

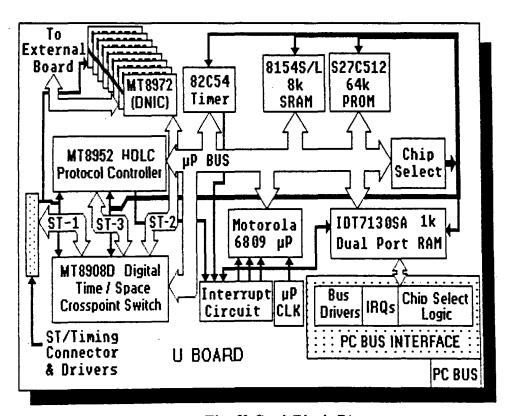

| Overview of the Hardware Design                   | 71 |

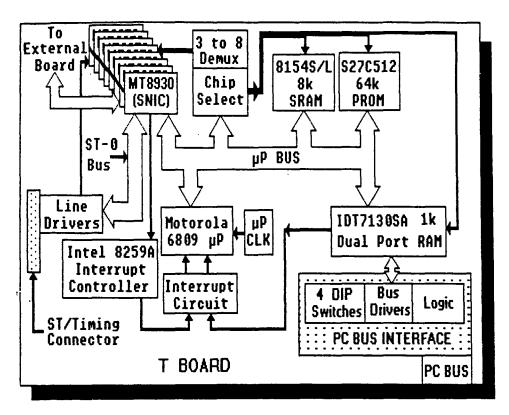

| The Main Switch Card                              | 72 |

| The External Board                                | 73 |

| The S/T-Interface Card                            | 74 |

| The MT8930 Subscriber Network Interface Circuit   | 75 |

| SNIC Interrupt Control                            | 77 |

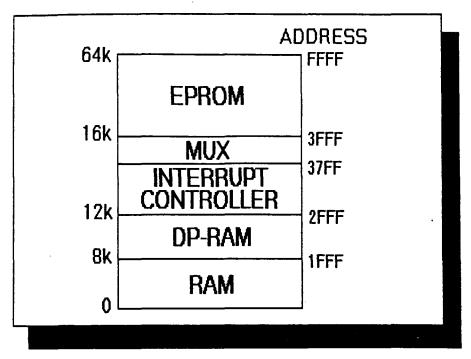

| S/T-Card Memory Mapping                           | 77 |

| The Microprocessor System                         | 78 |

| CHAPTER 5. THE DETAILED DESIGN OF THE U-INTERFACE |    |

| PC BOARD                                          | 79 |

| General Hardware Design Changes                   | 79 |

| U-Interface Operation                             | 80 |

| Component Interaction Changes                     | 80 |

| Additional Functionality                          | 81 |

| INTEL 8254 Programmable Interval Timer            | 81 |

| Operation                                    | 82  |

|----------------------------------------------|-----|

| Initialization                               | 82  |

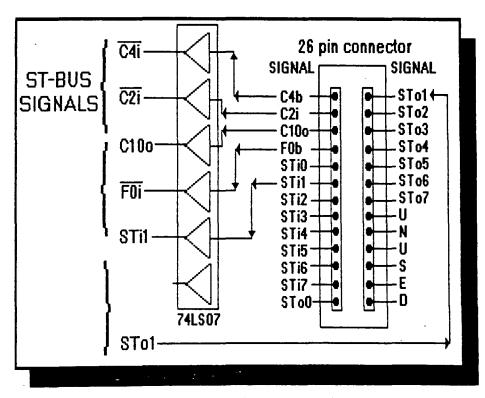

| The ST-BUS Interface                         | 83  |

| The 26 Pin Ribbon Connector                  | 83  |

| The Interface Circuit                        | 84  |

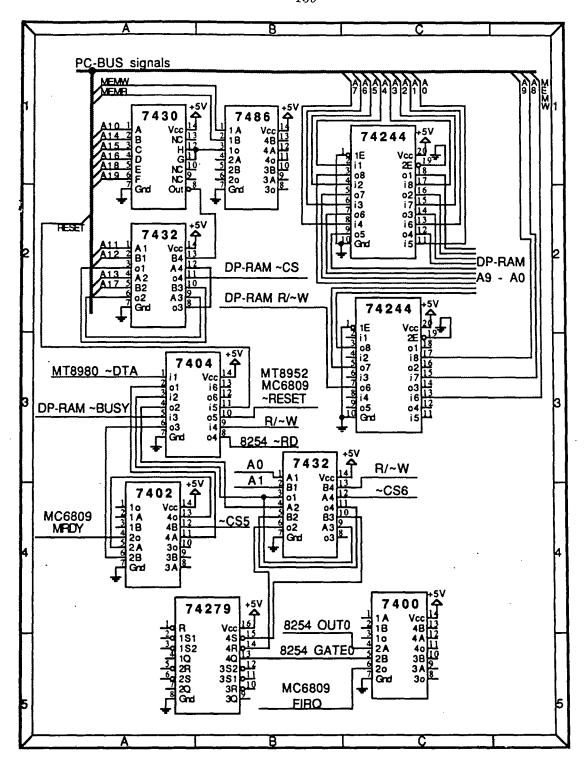

| The PC-BUS Interface                         | 84  |

| The PC-BUS Pin Assignments                   | 84  |

| IDT 7130SA/LA Dual-Port RAM                  | 84  |

| Supporting Circuits                          | 86  |

| The Microprocessor System                    | 87  |

| The MC6809                                   | 87  |

| Memory                                       | 90  |

| PAL Chip Select                              | 90  |

| CONCLUSION                                   | 94  |

| Status of the ISDN Central Office Project    | 94  |

| Interface Capabilities                       | 94  |

| Commercial Schematics                        | 94  |

| U-Interface Card Testing                     | 95  |

| Suggested Design Changes                     | 96  |

| The U-Interface Card                         | 96  |

| BIBLIOGRAPHY                                 | 99  |

| APPENDIX A. ACRONYMS                         | .01 |

| APPENDIX B. CCITT I-SERIES RECOMMENDATIONS 1 | .05 |

| I.100 | Series: | General Structure 108                                       | 5  |

|-------|---------|-------------------------------------------------------------|----|

|       | Section | 1: Frame of I-Series Recommendations - Terminology 105      | 5  |

|       | Section | 2: Description of ISDNs                                     | 5  |

| ;     | Section | 3: General Modeling Methods                                 | 5  |

| !     | Section | 4: Telecommunication Network and Service Attributes 109     | 5  |

| I.200 | Series: | Service Capabilities                                        | 6  |

| !     | Section | 1: Service Aspects of ISDNs                                 | 6  |

| ;     | Section | 2: Common Aspects of Services in an ISDN 100                | 6  |

|       | Section | 3: Bearer Services Supported by an ISDN 100                 | 6  |

| :     | Section | 4: Teleservices Supported by an ISDN                        | 6  |

| !     | Section | 5: Supplementary Services in an ISDN                        | 6  |

| I.300 | Series: | Overall Network Aspects and Functions                       | 7  |

|       | Section | 1: Network Functional Principles                            | 7  |

|       | Section | 2: Reference Models                                         | 7  |

|       | Section | 3: Numbering, Addressing, and Routing                       | 7  |

|       | Section | 4: Connection Types                                         | 7  |

|       | Section | 5: Performance Objectives                                   | 7  |

| I.400 | Series: | ISDN User-Network Interfaces                                | 8  |

|       | Section | 1: ISDN User-Network Interfaces                             | 8  |

|       | Section | 2: Application of I-Series Recommendations to ISDN User-    |    |

|       |         | Network Interfaces                                          | 8  |

|       | Section | 3: ISDN User-Network Interfaces: Layer 1 Recommendations 10 | 8  |

|       | Section | 4: ISDN User-Network Interfaces: Layer 2 Recommendations 10 | 8  |

|       | Section | 5: ISDN User-Network Interfaces: Layer 3 Recommendations 10 | 18 |

| Section 6: Multiplexing, Rate Adaptation, and Support of Existing |     |

|-------------------------------------------------------------------|-----|

| Interfaces                                                        | 109 |

| Section 7: Aspects of ISDN Affecting Terminal Requirements        | 109 |

| I.500 Series: Internetworking Between Various Networks            | 109 |

| I.600 Series: Maintenance Principles                              | 110 |

| A.2: OTHER RECOMMENDATIONS RELATED TO ISDN                        | 110 |

| APPENDIX C. U-CARD COMPONENT PIN ASSIGNMENTS                      | 111 |

| APPENDIX D. PARTS LISTS                                           | 121 |

| Main Card Parts List                                              | 121 |

| U-Interface Card Parts List                                       | 121 |

| External Board Parts List                                         | 121 |

| APPENDIX E. PAL AND CIRCUIT TEST PROGRAMMING                      | 126 |

| PAL Programming and Generated Files                               | 126 |

| PAL Program                                                       | 126 |

| PAL JED File                                                      | 127 |

| PAL Plot File                                                     | 128 |

| Circuit Test Programs                                             | 129 |

| SRAM and EPROM Pin Test                                           | 129 |

| DP-RAM Test                                                       | 129 |

| Switch, Controller, Timer and HDLC Interrupt Test                 | 130 |

## viii

| Daisy-Chain DNIC and Interrupt Tests | • | • | • | • | • | • | • | • | 133 |

|--------------------------------------|---|---|---|---|---|---|---|---|-----|

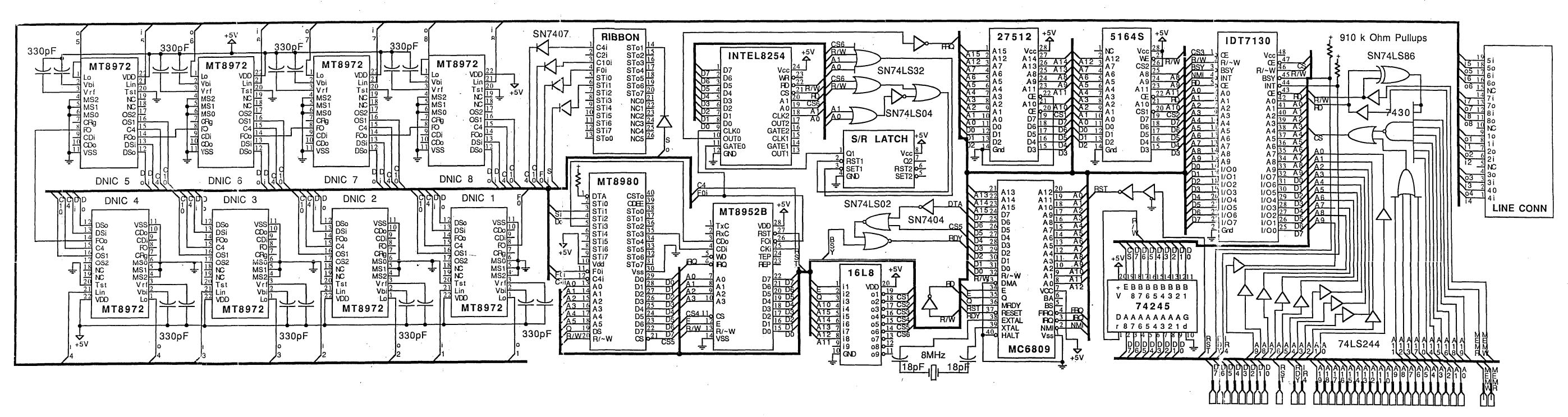

| APPENDIX F. U-CARD SCHEMATICS        | • |   |   |   |   |   |   |   | 138 |

| Gate to Chip Schematics              |   |   |   |   |   |   |   |   | 138 |

| PC Board Schematics                  |   |   |   |   |   |   |   |   | 138 |

## LIST OF TABLES

| Table 1.1:  | CCITT Study Groups                             | 14 |

|-------------|------------------------------------------------|----|

| Table 2.1:  | Possible ISDN Services and User Applications   | 19 |

| Table 2.2:  | ISDN Channel Types                             | 26 |

| Table 2.3:  | D-Channel Contention Priority Assignment       | 29 |

| Table 3.1:  | MT8980D Connection Memory Bits                 | 46 |

| Table 3.2:  | MT8980D Control Register Bits                  | 46 |

| Table 3.3:  | MT8972B Mode Definitions                       | 50 |

| Table 3.4:  | MT8972B Status Register                        | 51 |

| Table 3.5:  | MT8972B Control Register                       | 53 |

| Table 3.6:  | MT8972B Diagnostic Register                    | 54 |

| Table 3.7:  | MT8952 Register Addresses                      | 57 |

| Table 3.8:  | MT8952 FIFO: Received Byte Status              | 58 |

| Table 3.9:  | MT8952 FIFO: Receive FIFO Status               | 58 |

| Table 3.10: | MT8952 FIFO: Transmit FIFO Status              | 59 |

| Table 3.11: | MT8952 General Status Register Bit Definitions | 59 |

| Table 3.12: | MT8952 Interrupt Flag Register                 | 60 |

| Table 3.13: | MT8952 Control Register Bit Definitions        | 60 |

| Table 3.14: | MT8952 Timing Control Register                   | 61  |

|-------------|--------------------------------------------------|-----|

| Table 5.1:  | 8254 Interval Timer Control Register             | 82  |

| Table 5.2:  | The MC6809 Condition Code Register               | 89  |

| Table C.1:  | MT8910 DSLIC Pin Assignments                     | 112 |

| Table C.2:  | MT8952B HDLC Protocol Controller Pin Assignments | 113 |

| Table C.3:  | MT8972 DNIC Pin Assignments                      | 114 |

| Table C.4:  | The MT8980 DX Pin Assignments                    | 115 |

| Table C.5:  | Motorola 6809 Microprocessor Pin Assignments     | 116 |

| Table C.6:  | The 64k Byte EPROM Pin Assignments               | 117 |

| Table C.7:  | The 8k Byte SRAM Pin Assignments                 | 118 |

| Table C.8:  | The 1k Byte Dual-Port RAM Pin Assignments        | 119 |

| Table C.9:  | The 8254 Interval Timer Pin Assignments          | 120 |

| Table D.1:  | Main Card Components                             | 122 |

| Table D.2:  | S/T-Card Components                              | 123 |

| Table D.3:  | U-Card Components                                | 124 |

| Table D 4.  | External Components                              | 125 |

## LIST OF FIGURES

| Figure 1.1:  | Alexander Graham Bell's Telephone                  | 4  |

|--------------|----------------------------------------------------|----|

| Figure 1.2:  | Early Service and Switchboard Service              | 5  |

| Figure 1.3:  | Automatic Two Phase Switches                       | 6  |

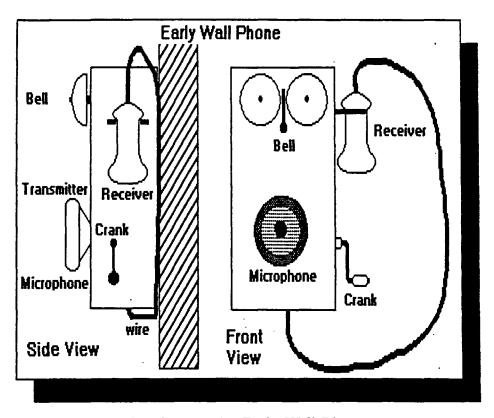

| Figure 1.4:  | An Early Wall Phone                                | 7  |

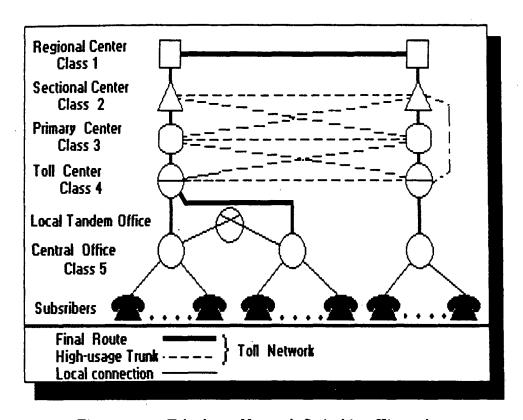

| Figure 1.5:  | Telephone Network Switching Hierarchy              | 9  |

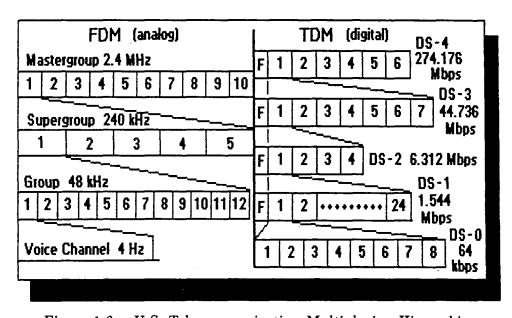

| Figure 1.6:  | U.S. Telecommunication Multiplexing Hierarchies    | 13 |

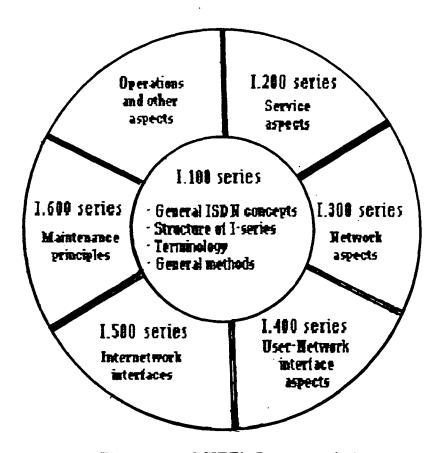

| Figure 1.7:  | CCITT's Recommendations                            | 15 |

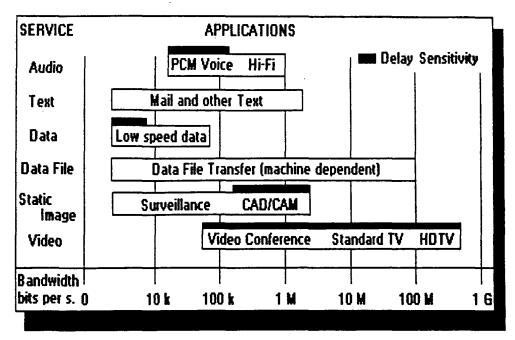

| Figure 1.8:  | Application Bandwidth Requirements                 | 17 |

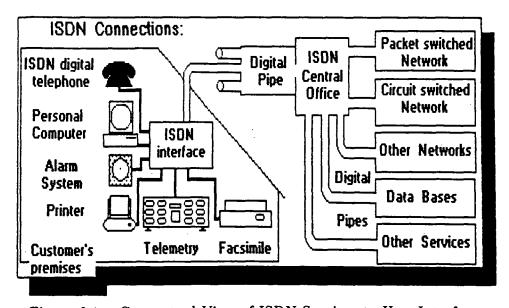

| Figure 2.1:  | Conceptual View of ISDN Services to User-Interface | 18 |

| Figure 2.2:  | ISDN User-Interfaces                               | 20 |

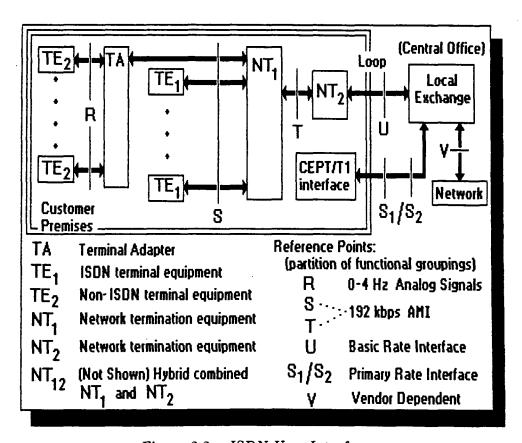

| Figure 2.3:  | ISDN Reference Model                               | 23 |

| Figure 2.4:  | ISO/OSI Model Interlayer Communication             | 24 |

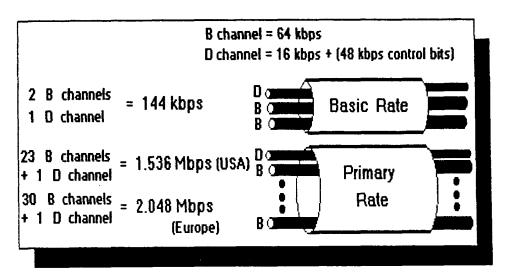

| Figure 2.5:  | ISDN User-Interface Transmission Rates             | 27 |

| Figure 2.6:  | ISDN Multi-point, Passive Bus Configuration        | 28 |

| Figure 2.7:  | ISDN S/T-Interface Bitstream Format                | 29 |

| Figure 2.8:  | ISDN U-Interface Bitstream Format                  | 30 |

| Figure 2.9:  | LAP-D Frame Format                                 | 31 |

| Figure 2.10: | LAP-B Frame Format                                 | 32 |

| Figure 3.1:  | The Original ISU Central Office Hardware Design | 37 |

|--------------|-------------------------------------------------|----|

| Figure 3.2:  | The ST-BUS BRI Channels and Timing              | 38 |

| Figure 3.3:  | The ST-BUS Clock Signal Generation Diagram      | 40 |

| Figure 3.4:  | PC-Bus Interface Block Diagram                  | 41 |

| Figure 3.5:  | ST-BUS Channels at the PRI                      | 43 |

| Figure 3.6:  | The MT8980D Functional Block Diagram            | 44 |

| Figure 3.7:  | C-Channel DNIC Control Routing                  | 48 |

| Figure 3.8:  | Line Signaling Waveforms                        | 52 |

| Figure 3.9:  | The MT8952 Functional Block Diagram             | 56 |

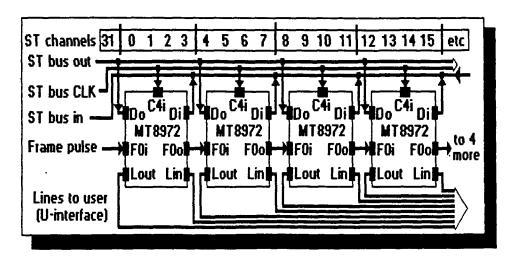

| Figure 3.10: | DNIC Daisy-Chain Diagram                        | 64 |

| Figure 4.1:  | Central Office Block Diagram                    | 71 |

| Figure 4.2:  | The Main Switch Card Block Diagram              | 72 |

| Figure 4.3:  | The External Board Block Diagram                | 73 |

| Figure 4.4:  | The T-Interface Card Block Diagram              | 74 |

| Figure 4.5:  | S/T Card Memory Mapping Diagram                 | 78 |

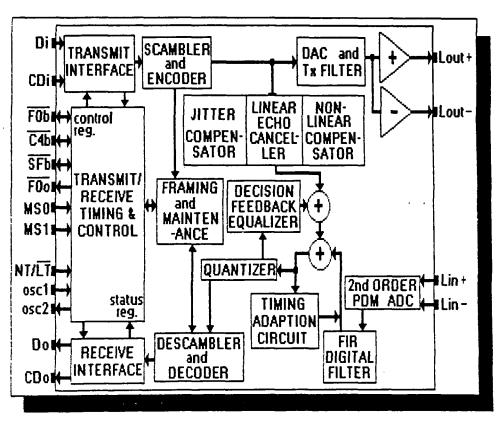

| Figure 5.1:  | The U-Card Block Diagram                        | 79 |

| Figure 5.2:  | The ST-BUS Interface Block Diagram              | 83 |

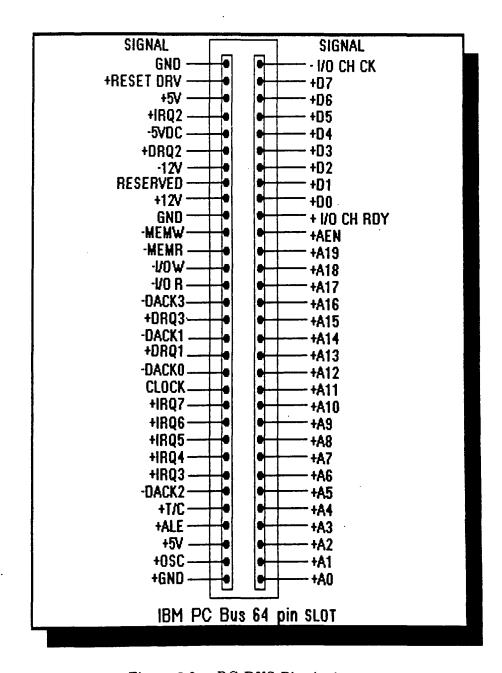

| Figure 5.3:  | PC-BUS Pin Assignments                          | 85 |

| Figure 5.4:  | The PC-BUS Interface Block Diagram              | 86 |

| Figure 5.5:  | MC6809 Registers                                | 88 |

| Figure 5.6:  | U-Card Memory Mapping                           | 91 |

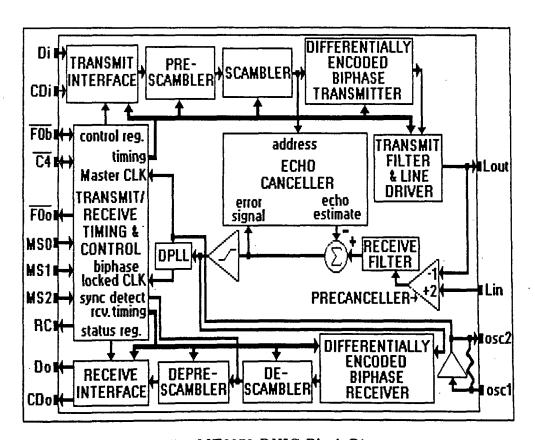

| Figure 5.7:  | MT8972 DNIC Block Diagram                       | 92 |

## xiii

| Figure 5.8: | MT8910 DSLIC Block Diagram     |  | • | • | • | • | <br>• | • | • | • | • | • | 93  |

|-------------|--------------------------------|--|---|---|---|---|-------|---|---|---|---|---|-----|

| Figure F.1: | U-Card Latch and Other Logic . |  | _ |   |   |   |       |   |   |   |   |   | 139 |

#### INTRODUCTION

ISDN is an evolving global networking concept to provide a variety of services using a standard user interface over a common communication medium, namely the existing telecommunications system. Presently, separate lines are needed to provide services such as coaxial cable T.V. The concept began in and has been actively pursued by the telecommunications industry through the CCITT.

Chapter 1 includes a brief technical development history of the telephone based telecommunications system to its current status, the evolution of ISDN from its conception to its present status, and the role of the central office. Topics covered include:

- The initial inefficient techniques using point-to-point pairs;

- The birth of a circuit switching central office with manual switchboards;

- The advent of automatic switches for the central office;

- The topology of the modern telephone network;

- Other types of telecommunication networks;

- The control of telecommunication networks;

- The role of the CCITT in the development of ISDN;

- Setbacks to the rapid realization of a global ISDN;

- And the development of ISDN products and services;

A formal description of ISDN standards and protocols and the role of the CCITT in their development is provided in Chapter 2. Also covered is a brief description of possible user applications and bandwidth requirements.

The initial effort of building an IBM XT PC based ISDN central office, one of a number ISDN research projects within the Computer Engineering Department at Iowa State University, is detailed in Chapter 3. Other ISDN projects include:

- A senior design team project of building an ISDN digital telephone with enchancements. The telephone is designed to interface to the central office at the U-Interface;

- A graduate student project of designing and building an ISDN B channel multiplexer. The device is to multiplex eight asynchronous lines into a single B channel;

- An independent senior design project of building an ISDN TA;

- A graduate student project of designing and building a high speed ISDN to Ethernet gateway;

- And a graduate level course that included writing the software required to implement ISDN protocols in the central office.

Chapter 4 covers the revision of the original central office design goals, the division of design responsibilities, and a description of the various hardware segments of the revised design. All segments except the U-Interface are covered in some detail.

Chapter 5 furnishes a description of the design of the U-Interface card. The additions to the original design are covered in detail, as well as an overview of the card's functionality. The Conclusion deals with the changes required to make the U-interface conform to recently passed standards, the existing state of the central office design, hardware testing procedures, results of the testing, and suggestions pertaining to the expandability of the design.

## CHAPTER 1. THE EVOLUTION OF TELECOMMUNICATIONS

In the beginning were the words, "Mr. Watson, please come here. I want you." That was the initial spark leading to the current explosion in communications. The telecommunications industry has steadily evolved over the last 115 years, continuously changing due to technological advances and influx of customers.

## Telephone Communications

## Inventions Spawn Growth

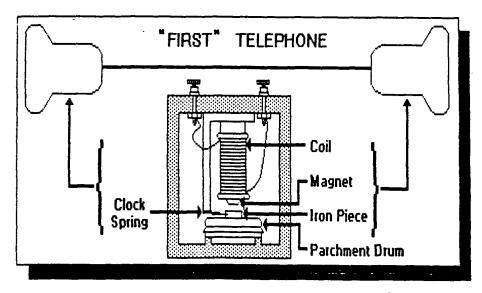

Figure 1.1: Alexander Graham Bell's Telephone

The Telephone Although a German scientist, Johann Philipp Reis, is believed to have invented the telephone, and a Chicago American, Elisha Gray, filed a patent the same day as Alexander Graham Bell, Mr. Bell has been historically recognized as the inventor of the device [28]. In January of 1876 in Boston, Massachussetts, the first telephone conversation took place between Mr. Bell, in the attic of his home, and his assistant Mr. Thomas Watson, on the ground floor. Immediately thereafter Mr. Bell sketched the design of his device, as in Figure 1.1, and applied for a patent, which was granted on his 29th birthday.

In 1877 Thomas Alva Edison of the USA invented the carbon microphone, as did Englishman Professor David Edward Hughes, who received the majority of credit for the invention in 1878. Therefore today's telephones contain a microphone transmitter and an electro-magnetic earphone receiver. Also in 1877 the first telephone service began as point-to-point pairs in Charleston, Massachussetts.

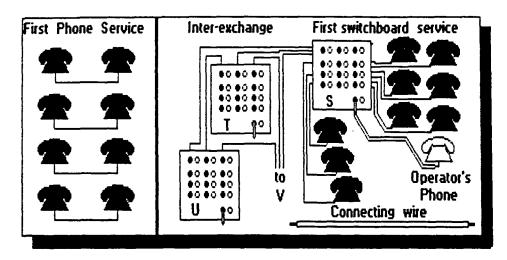

Figure 1.2: Early Service and Switchboard Service

Switchboards In 1878 a manually operated switchboard, the first telephone exchange and central office, was opened in New Haven, Connecticut, allowing eight subscribers to connect in pairs, as depicted in Figure 1.2. To respond to demand, larger switchboards were built and put in service. Coupled with intercity and trans-Atlantic coaxial cable distribution lines, switchboards allowed long distance point to point communication.

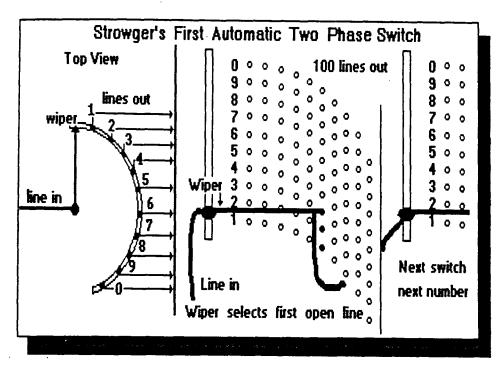

Figure 1.3: Automatic Two Phase Switches

Automatic Switches The automatic switch was invented by Mr. Almon B. Strowger in 1889, and allowed local direct dialing of other subscribers. The switch, illustrated in Figure 1.3, consisted of two parts for each number dialed, a column selector corresponding to the number dialed and a line selector which selected the first available, non-busy, line in the column of number dialed. Modern microprocessor

driven switches, using digital electronics and logic, are presently replacing the old electro-mechanical switches [24]. These new switches are implemented on a VLSI chip. They require less physical space and perform a wider variety of functions, such as buffering of information. They exhibit improved response time, without signal jitter due to the electro-mechanical switch bouncing [23].

Figure 1.4: An Early Wall Phone

Subsequent Changes to Telephones In conjunction with electro-mechanical switches came telephones with dials. The dials replaced the crank generators, represented in Figure 1.4, used to call switchboard operators. Subscribers were assigned telephone numbers, so that a series of these switches could connect two subscibers,

using dial signals. Although the advent of automatic switches replaced the need for switchboard operators, switchboards remained in use in parts of the USA for local or long distance calls and in some businesses into the early 1970's [28].

Logic enhanced switches led to touch tone telephones, replacing the number dial used to generate signals for the switch wiper. However, touch tone telephones retained the use of analog based communication. The modern switches being placed in service have led to the development of digital based communication telephones. Although prior to the advent of these telephones, telephones used digital electronics to provide a wide variety of services, such as auto-redial, speed dialing, and message retention.

#### Modern Telecommunication Networks

Network Topology The typical topology of a telecommunications network, see Figure 1.5, consists of a backbone of central offices or switching centers, which are connected together, either directly, or indirectly through a tandem office via interoffice circuits. Each central office serves subscribers within a few kilometer radius. Several thousand subscribers may be connected to a single central office. Switches in various central offices must have the ability to communicate information to switches in distant central offices in order to perform efficient routing when establishing connections.

Equipment Not all telephone companies, worldwide, have modern equipment. Service varies not only between countries and companies, but within the geographical areas of the countries themselves. Third world countries and rural areas, where demand is small, may have used and antiquated equipment. Services offered in an

Figure 1.5: Telephone Network Switching Hierarchy

area are dependent upon the network equipment in that area.

Ownership and Control Most telephone companies outside of the USA are owned by the government, and virtually all are regulated by the governments of the countries in which they are located. In the USA early telecommunication companies were small, local, free enterprise entities. AT&T eventually monopolized the long distance distribution and most of the major local markets. The companies it didn't own, it could control indirectly because of its monopoly on the rest of the market.

Consequently, the FCC was created to regulate AT&T's activities and tariffs. Based upon an anti-trust lawsuit filed by the federal government in 1974, AT&T was forced to split its vast holdings in 1984. This resulted in the world's only free enterprise telecommunication's system, as well as a certain amount of chaos in the industry overall, since AT&T was the industry's leader[3].

Modern Free Enterprise System Although the splitting of AT&T and its 22 service subsidiaries theoretically brought reduced rates through competition, it also destroyed the previously uniform approach to introduce new technology and services. In order to compete as a long distance carrier and to realign its objectives and personnel, AT&T temporarily shelved some programs such as ISDN[3]. Standards enabling a uniform approach to a diversified problem were forsaken in lieu of profit in the new USA competitive marketplace.

The final results were:

- seemingly increased rates or no noticeable reduction for the consumer;

- seven large local distribution companies and several competing long distance

carriers;

- non-uniform implementation of a variety of new services;

- and the introduction of switches from various vendors that could not communicate outside of their own vendor's products.

Uniformity of equipment and enhanced service implementation became non-existent and consequently integration is more complicated.

#### **Telecommunications**

#### **Definition of Telecommunication**

The formal definition of telecommunications is the sending and receiving of messages over a distance by electrical methods [24]. Telephone networks are the most widespread, not only, in terms of geographic area and availability, but also, in terms of potential capacity and usage. But telecommunications does not only consist of telephone networks.

#### Other Forms of Telecommunication

Analog Entities The first telegraph was in service by 1839 in London, England. The wireless telegraph, which preceded public radio's inception in the 1920's, dates back to the 1890's. Public television became widespread in the United States after World War II, and satellite communication was introduced in the early 1960's [28]. Finally, access to coaxial cable television, Cable TV, became widespread during the late 1970's, and video teleconferencing facilities were available in the 1980's [24].

Computer Networks ARPANET, the first major computer network, originated in 1969 as a research network under the influence and control of ARPA, an agency of the U.S. Department of Defense. It used leased telephone lines to transfer information, data, between its original four nodes, geographical sites. By 1975 it had grown into an extensive network, and was put under the control of the Defense Communications Agency [4]. In 1974 IBM announced its development of SNA, the first distributed packet switched network, and made it commercially available [3].

#### Integration of Services

#### Evolution of the Concept

The Analog Environment In 1959 H. E. Vaughan proposed ISN, an integrated services network, which would bring most major telecommunication services into businesses and residences via public telephone lines [15]. The vast distribution network of the telephone industry, and the advances in and widespread use of automatic switches made this idea feasible. However the technology in 1959 was based upon analog signaling, and was, not only, unable to filter out noise between repeaters, but also, propagated noise end to end.

Digital Technological Advancements Digital multiplexing provided greater bandwidth utilization than analog FDM, as depicted in Figure 1.6 [14]. Advances in TDM, VLSI circuits using PCM for analog to digital and digital to analog conversion for digitized voice transmission, VLSI circuit implementation of smart switches, fiber optic transmission techniques and cables, and digital noise filtering techniques at repeaters made fully integrated services more feasible. The inherent delay and echo

Figure 1.6: U.S. Telecommunication Multiplexing Hierarchies

Table 1.1: CCITT Study Groups

| NUMBER | TITLE                                                         |

|--------|---------------------------------------------------------------|

| I      | Definition, operation and quality of service aspects of       |

|        | telegraph, data transmission and telematic services           |

| II     | Operation of telephone network and ISDN                       |

| III    | General tariff principles including accounting                |

| IV     | Transmission maintenance of international lines, circuits and |

|        | chains of circuits; maintenance of automatic and              |

|        | semi-automatic networks                                       |

| V      | Protection against dangers and disturbances of                |

|        | electromagnetic origin                                        |

| VI     | Outside plant                                                 |

| VII    | Data communications networks                                  |

| VIII   | Terminal equipment for telematic services                     |

| IX     | Telegraph networks and terminal equipment                     |

| X      | Languages and methods for telecommunications applications     |

| XI     | ISDN and telephone network switching and signaling            |

| XII    | Transmission performance of telephone networks and terminals  |

| XV     | Transmission systems                                          |

| XVII   | Data transmission over the telephone network                  |

| XVIII  | Digital networks including ISDN                               |

problems of digitized voice transmission became history.

CCITT Preference Is Digital In 1971 during a meeting of the CCITT's Study Group XI, assigned to study and to recommend standards for switching and signaling, shown in Table 1.1, the term ISDN was first introduced. Despite the fact that disputes continued until 1988 over whether an integrated service should be implemented in analog, digital, or a combination of the two, the CCITT pushed the ISDN concept, founding Study Group XVIII in the late 1970's specifically for the purposes of setting goals and studying standard proposals for ISDN [15].

#### The Evolution of ISDN

#### CCITT's Standards

Figure 1.7: CCITT's Recommendations

From 1980 to 1984 the I-series standards were partially developed and published. By 1984 the CCITT had the majority of its study groups involved in developing standards for ISDN, and with the influx of fiber cable into major distribution lines directed focus on the development of B-ISDN standards. More standards were adopted in 1988, with 2B1Q the most recent [16].

#### Major Setback

However the industry's leader, AT&T, which initially had been totally committed to ISDN, was derailed temporarily by the consequent upheaval of reorganization of the company due to Judge Green's decision in 1982 to split the company. This as previously outlined, not only led to a delay in implementation in the United States, but also slowed the research and standards process. Many of ISDN's services were implemented by providers outside of the singular approach of the CCITT's ISDN standards [2].

#### **Evolution of Products and Services**

The first time-division digital switch was developed by Western Electric, an AT&T subsidiary, in 1976, and ISDN digital phones appeared in the 1980's. Part of AT&T's 800 service is implemented in ISDN, and a renewed effort is being made due to potential business LAN and WAN applications and high rate data transfer from remote PC's. Also the DOD has expressed an interest in the ISDN backbone concept.

Furthermore fiber optics based B-ISDN, in the research stage, has the potential of offering a wider variety of services to a wider range of subscribers due to the high bandwidth capabilities of fiber cable. Some applications and their bandwidth requirements are outlined in Figure 1.8 [1]. Layer-2 and Layer-3 standards are similar to ISDN's, however due to vast differences in Layer-1 mediums, B-ISDN standards in this layer use different multiplexing and transmission techniques. SONET with a rate of 155.52 Mbps and ATM have been adopted as standards [7].

Figure 1.8: Application Bandwidth Requirements

#### CHAPTER 2. ISDN

#### Services

ISDN is an evolving technology designed to provide a set of common user interfaces to a wide range of telecommunication and networking services on both a local and a global basis via telephone distribution systems. Some of the user services that ISDN is expected to provide are outlined in Table 2.1 [14].

Figure 2.1: Conceptual View of ISDN Services to User-Interface

User to services interfaces are conceptually represented in Figure 2.1. ISDN services are available to the user only through the user's central office. Central offices

Table 2.1: Possible ISDN Services and User Applications

| ISDN SERVICE | APPLICATIONS                                         |

|--------------|------------------------------------------------------|

| Circuit      | Basic telephone service                              |

| Switched     | Call screening via caller's number recognition       |

| Services     | -                                                    |

| Services     | call tracing                                         |

|              | Selective call forwarding                            |

|              | Junk facsimile recognition (deny advertizing access) |

|              | Elelectronic funds transfer                          |

|              | Video transactions                                   |

|              | Video telephones                                     |

|              | Nuisance (also runaway or kidnapped children)        |

|              | Automatic call waiting                               |

| Packet       | Elelectronic mail enhancements                       |

| Switched     | Conference calls                                     |

| Services     | Video teleconferencing                               |

|              | Telemetry (911)                                      |

|              | Automatic call distribution based on caller's number |

| Networking   | PBX networks (LANs)                                  |

| Services     | LAN interconnections                                 |

|              | Public network access                                |

|              | Automatic voice response to database access          |

|              | Database caller authorization                        |

|              | Remote high speed data transfer                      |

|              | Programmed education                                 |

| Other        | Automatic call return                                |

| Services     | Selective (personalized) messages                    |

|              | Extension of business services into homes            |

|              | Automatic dial telemarketing (until response)        |

|              | Automatic caller data retrieval                      |

|              | (previous communication history)                     |

|              | Security systems                                     |

in the United States are in the process of conversion to offer ISDN services, however 200 ISDN subscribers are necessary to make conversion cost effective. Charges are about double that of normal telephone service, but the cost of on premise equipment appears to be the primary prohibitive factor. A minimal cost of equipment with network termination would run in excess of two thousand dollars.

#### **Functional Architecture**

Figure 2.2: ISDN User-Interfaces

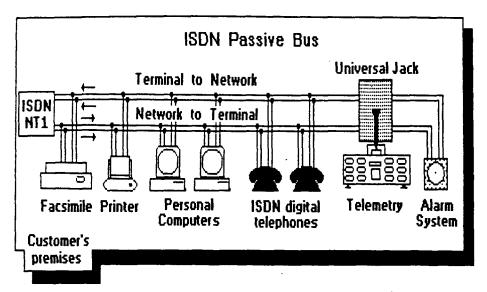

An ISDN topology depicting both equipment and interfaces, reference points, is illustrated in Figure 2.2. Reference point designations date back to the advent

of switchboards, see Figure 1.2. The exact definition of the interface between the customer's premises and the central office, however, is not clearly defined, due to the scope of implementation on the customer's premises [16].

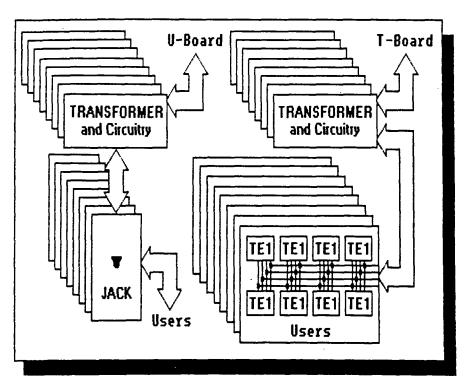

European and North American (including Japan) standards differ in the network termination points at the customer's premises. In Europe NT1 terminates the network. NT2 functions are performed at the central office via the T-Interface. The North American customer's installation includes the NT2, so that the central office supports the U-Interface. The ISU central office supports both the S/T-Interface, a combination of the S-Interface and the T-Interface, and the U-Interface.

Equipment, depicted in Figure 2.2, is defined as follows:

- 1. TE1. A customer premise device supporting the ISDN S-Interface.

- 2. TE2. A customer premise device not supporting the ISDN S-Interface.

- 3. TA. A device supporting the ISDN S-Interface between TE2 equipment and ISDN's NT1.

- 4. NT1. Customer premises network termination equipment supporting the Physical Layer protocols as outlined in Figure 2.3.

- 5. NT2. Network termination equipment supporting the Data Link and some Network Layer protocols as outlined in Figure 2.3.

The NT2 could stand alone as a PBX or be combined with an NT1 to form a hybrid NT12, network termination device, supporting the S/T-Interface. The interfaces depicted in Figure 2.2 are defined as follows:

1. R - Twisted pair with analog voice signal, 0-4 hz rate.

- 2. S Two twisted pairs with ISDN digital bitstream, 192 kbps rate.

- 3. T Two twisted pairs with ISDN digital bitstream, 192 kbps rate.

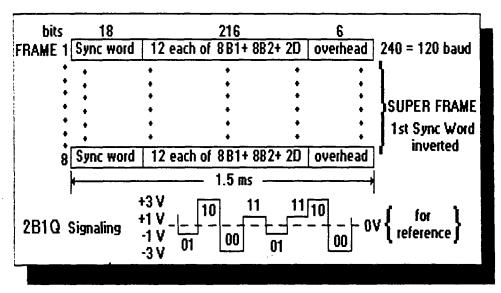

- 4. U Twisted pair with ISDN 2B1Q bitstream, 160 kbps, 80 baud rate.

- 5. S1/S2 T1 or fiber optic cable with PRI rate of 2.048 or 1.544 Mbps.

- 6. V Optional and vendor dependent.

#### Standards

#### **CCITT I-Series Recommendations**

The CCITT's goal is that the set of ISDN standards and protocols being developed will eventually be the standards and protocols of all wire based telephone distribution systems worldwide. The goal for fiber based distribution systems is the total adoption of B-ISDN standards and protocols. Far in the future, fiber will replace twisted pairs and ISDN will be phased out in lieu of B-ISDN, but there is no immediate danger of that due to the cost of converting all existing twisted pairs to fiber optic cable.

ISDN standards are to be implemented in both on premises subscriber's ISDN equipment and the various telephone systems' offices' equipment. The CCITT's evolving, I-series Recommendations as of 1990 are outlined in detail in Appendix A. The I-series recommendations are quite extensive, covering not only all technical aspects of ISDN, but also committee procedures and service rates.

### ISDN Reference Model

| ISO/OSI<br>Reference Model                                         | ISD<br>Layered Arc                                 |         |                                                    |                      |                   |                |

|--------------------------------------------------------------------|----------------------------------------------------|---------|----------------------------------------------------|----------------------|-------------------|----------------|

| Application Layer Presentation Layer Session Layer Transport Layer | End-to-End<br>User<br>Signaling<br>(to be defined) |         | ISO - CCITT<br>Existing Standards<br>(Under Study) |                      | ards              |                |

| Network Layer                                                      | 1.451<br>call control                              | X.25    | Further<br>Study                                   |                      |                   | X.25<br>packet |

| Data Link Layer                                                    | 1.441 (HD                                          | LC L/   | AP-D)                                              | •                    |                   | X.25<br>LAP-B  |

| Physical Layer                                                     | Physical Layer Layer 1 (1.430, 1.431)              |         | 2B1Q                                               |                      |                   |                |

| , 5.22. 23/61                                                      | Signaling P                                        | acket T | elemetry                                           | Circuit<br>Switching | Leased<br>Circuit | Packet         |

|                                                                    | D Channel                                          |         |                                                    | Channe               |                   |                |

Figure 2.3: ISDN Reference Model

Link-to-Link Layers The ISDN reference model best depicts the technical standards and protocols of interest. The ISDN reference model is based upon the bottom three layers of the OSI/ISO reference model, and is depicted in Figure 2.3. There are two basic reasons for this. The CCITT, the largest proponent of ISDN, is concerned primarily with the implementation aspects of standards and protocols in telephone networks. This translates to the bottom layers of the OSI/ISO model.

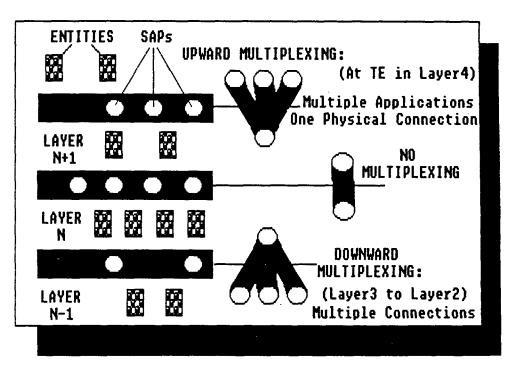

As depicted in Figure 2.4, services are provided to a layer by the layer directly below it via SAPs. Primitives are used in the communication between the layers to identify the service requested or the response. Data, information, and options are passed as parameters to the primitives. Headers are added at each of the lower four

Figure 2.4: ISO/OSI Model Interlayer Communication

layers to the data.

End-to-End Layers The Application Layer through the Transport Layer of the OSI/ISO model are end-to-end layers, and define the protocols required for the exchange of information between same layer entities on two communicating host machines. Protocols for these layers will be developed as businesses become interested in implementing ISDN LANs and WANs. As yet, a complete set of standards has not been developed for these layers by the ISO in the OSI reference model.

# The Physical Layer

# **Specified Functions**

As illustrated in Figure 2.3, I.430 (BRI) and I.431 (PRI) specify the Physical Layer standards. The functions specified in these user-network interface standards are [14][16]:

- Activation and deactivation of the physical circuit, reducing power consumption

when the channels are idle.

- Contention resolution on the D channel for point to multipoint configurations.

- Encoding of digital transmission via AMI at the S/T interface and 2B1Q at the U-Interface.

- Faulty terminal identification and isolation, via loopback testing.

- Full duplex transmission of B and D channels.

- Multiplexing of channels to obtain BRI and PRI transmission requirements.

- Power feeding from the NT, source, to the TE, sink.

- Terminal identification.

### Transmission Rates

Table 2.2: ISDN Channel Types

|                             |                              | <del></del>   |

|-----------------------------|------------------------------|---------------|

| CHANNEL                     | PURPOSE                      | BIT RATE      |

| В                           | Bearer Services              | 64 kbps       |

| D or <i>D</i> <sub>16</sub> | Signaling and Packet Mode    | 16 kbps (BRI) |

| $D_{64}$                    | Data                         | 64 kbps (PRI) |

| $H_0$                       | Six B channels               | 384           |

| $H_1$                       | All Available $H_0$ Channels |               |

|                             | $H_{11}$ (24B)               | 1536 kbps     |

|                             | $H_{12}$ (30B)               | 1920 kbps     |

| $H_2$                       | Proposed B-ISDN              |               |

|                             | $H_{21}$                     | 32.768 Mbps   |

|                             | $H_{22}$                     | 43-45 Mbps    |

| $H_4$                       | Proposed B-ISDN              | 132-138 Mbps  |

At the Physical Layer in the model, ISDN's transmission medium consists of local digital signaling over twisted pair wires and long-haul multiplexed digital signaling over T1 carriers or fiber cables where available. Due to the influx of fiber distribution lines and fiber based LANs, B-ISDN standards are being developed. ISDN standards specify three basic channel types as detailed in Table 2.2. Interoffice signaling, CCIS, is out-of-band at the rate of 800 bps on a separate network [16].

### User-Interface Rates

Basic Rate Interface Combinations of B and D channels compose two user interfaces, BRI and PRI. Conceptually to the user, these can be thought of as digital

Figure 2.5: ISDN User-Interface Transmission Rates

pipes as depicted in Figure 2.5. The basic rate channel's effective rate is 144 kbps, with 48 kbps used for overhead, control and contention resolution at the S and/or T interfaces on the customer's premises, as detailed in Figure 2.2. B channels are used for voice and data, while the D channel is used for data, such as a virtual terminal, and for signaling, such as control of the B channels [14].

Primary Rate Interface Unlike the basic rate interface, which is standard worldwide, the primary rate interface is defined by two standards. The North American primary rate channel uses 8 kbps as framing or synchronization bits, one every 193 bits. The  $D_{64}$  channel is used for data and control. The European primary rate looses 64 kbps in overhead, leaving a maximum effective data transfer rate of 1.984 Mbps less framing. The North American maximum effective data transfer rate is 1.536 Mbps less framing [16].

# Reference Point Signaling Standards

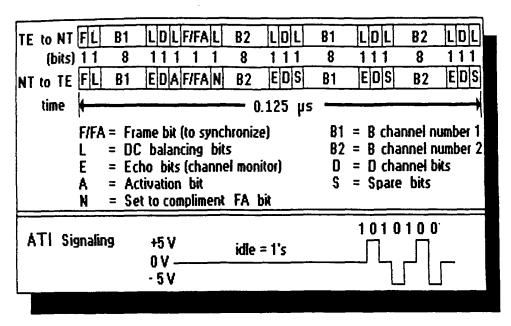

ISDN standards stipulate different signaling techniques at the U and S/T reference points, as depicted in Figure 2.2. Not only are the rates different but so are the voltages and techniques. The U reference point signals each designate two bits, while the S and T reference points only one. Also the interleaving of D and B channels is different.

Figure 2.6: ISDN Multi-point, Passive Bus Configuration

S/T-Interface Signaling Standard The bitstream at the S and T reference points, as illustrated in Figure 2.7, supports the BRI of 144 kbps plus control and overhead for a total rate of 192 kbps. A single NT can support up to eight TEs. These can be configured as point-to-point, TE to NT, or point-to-multipoint, such as a passive bus, diagrammed in Figure 2.6.

E bits echo the incoming D channel bits and are used to resolve contention for the D channel between competing TEs. The TEs monitor the E bits and after waiting

Figure 2.7: ISDN S/T-Interface Bitstream Format

for either 8, 9, 10, or 11 successive logical 1's, depending upon a TE's priority and the type of information it has to transmit, the TE transmits a logic 0 to request the channel. If a conflict occurs, the TE must backoff and renew the waiting process. Priority is based upon which TE last used the channel and is used to prevent starvation, as depicted in Table 2.3.

Table 2.3: D-Channel Contention Priority Assignment

| PRIORITY    | This TE Last Used the Channel | WAIT PERIOD |

|-------------|-------------------------------|-------------|

| Data/Signal | No                            | 8           |

|             | Yes                           | 9           |

| Telemetry   | No                            | 10          |

|             | Yes                           | 11          |

Logic 1 transmits at 0 V to conserve power when the channels are idle. Logic 0 transmissions alternate between positive and negative voltages, and therefore con-

flicts are easily detected. Pseudo-tenary signaling, also referred to as alternate zero inversion, AZI, is specified in the standards and is illustrated in Figure 2.7 [16].

Figure 2.8: ISDN U-Interface Bitstream Format

2B1Q: U-Interface Signaling Standard The U reference point bit rate is 160 kbps, with two bits represented in each signal, as illustrated in Figure 2.8. Therefore the signal rate is 80 kbaud. While this is far less than the S/T bit rate of 192 kbps, it is still adequate to carry the basic rate of 144 kbps. While the S/T bitstream B and D channel interleaving is 8 B1, 1D, 8 B2, 1D, the U bitstream interleaving is 8 B1, 8 B2, 2D.

# The Data Link Layer

As illustrated in Figure 2.3, I.441 LAP-D and X.25 LAP-B are standards approved for the D and B channels respectively in the Data Link Layer, Layer 2 of the

CCITT Recommendations. The D channel supports control signaling, packet switching, and telemetry via LAP-D. The B channel supports circuit switching, leased circuits, and packet switching via LAP-B. The B in LAP-B does not denote the B channel but signifies balanced signaling. LAP-B is a subset of HDLC, and LAP-D is based upon LAP-B, as referenced in Figures 2.10 and 2.9 [8].

### LAP-D: The D Channel Interface

LAP - D (Based on LAP - B) Octets 1 2 2 260 maximum 2 Flag Address Control FCS Flag Data EA C/R SAPI TEI Sub-fields EA Flag = Sequence °01111110° 6 bits (uses bit stuffing) #5 "1's" elsewhere EA = Address extension bits add a °0° = Command / Response bit SAPI = Service Access Point Identifier FCS = Frame Check Sequence TEI = Terminal Endpoint Identifier or CRC code NOTE: Data Link Connection Identifier (DLCI) = SAPI + TEI

Figure 2.9: LAP-D Frame Format

Frame Format The LAP-D frame format is illustrated in Figure 2.9, above. The flags are used for frame synchronization, due to the variable length data field and the ability to extend destination addresses of both the SAP and the TE. The EA bit is set from '0' to '1' to extend these address fields, the SAPI and the TEI, which combined form the total data link destination address. The FCS field performs error detection. Bad packets are discarded, as are packets when only a singular flag is

detected in the bitstream. To avoid this happening naturally in the address, control, data, and FCS fields, bitstuffing is used as outlined in the figure.

Functions The primary functions of the LAP-D, I.441, protocols are as follows:

- Establish, maintain, and terminate Data Link connections for both channels.

- Handle multiplexing at the customer's premises, between TEs and within a single TE running multiple applications, or a single application requiring multiple simultaneous traffic types.

- Provide error detection as previously defined.

LAP-B: The B Channel Interface

|                                                                                                      | ISO's X.25 LAP-B (Balanced Mode) (A subset of HDLC) |                                                  |             |     |             |        |      |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-------------|-----|-------------|--------|------|

| Octet                                                                                                | 1_                                                  | 1 or more                                        | 1 or 2      |     | Unspecified | 2 or 4 | 1    |

|                                                                                                      | Flag                                                | Address                                          | Control     |     | Data        | FCS    | Flag |

| Address = identifies a secondary station (either transmitter or receiver) Flag = Sequence *01111110* |                                                     | Control Field:<br>(3 types of<br>I-Frame = Infor | •           | ama |             |        |      |

| (uses bit stuffing) FCS = Frame Check Sequence or CRC code                                           |                                                     | S-Frame = Supe<br>U-Frame = Unur                 | rvisory Fra | ame |             |        |      |

Figure 2.10: LAP-B Frame Format

The LAP-B frame is outlined in Figure 2.10. Like LAP-D, bit stuffing is used to keep the synchronization flags unique. Error detection is also provided in the FCS

field using the CCITT defined polynomial [19]:

$$G(x) = x^{16} + x^{12} + x^5 + 1.$$

The definition of the control field frame types are as follows [8]:

- I-Frame contains normal data and information.

- S-Frame contains control information, such as acknowledgements.

- U-Frame contains options and network management information.

Packetized data is exchanged over the B channel, whether the connection is circuit switched, leased, or packet switched. X.25 levels 2 and 3 are used to establish a virtual circuit and exchange packets.

### The Network Layer

The accepted standards for Layer 3, as outlined in Figure 2.3, are I.451, or Q.931, and ISO's X.25. The functions performed at the Network Layer are [12]:

- (a) The processing of primitives for communicating with the Data Link Layer.

- (b) The generation and interpretation of Layer 3 messages for peer-level communication.

- (c) The administration of timers and logical entities (e.g. call references) used in the call control procedures.

- (d) The administration of access resources including B channels and packetlayer logical channels (e.g. Recommendations X.25).

(e) Checking to ensure that services provided are consistent with user requirements.

General functions that may also be performed are:

- (a) Routing and relaying.

- (b) Network connection control.

- (c) Conveyance of user-to-network and network-to-user information.

- (d) Network connection multiplexing.

- (e) Segmenting and Reassembly.

- (f) Error detection.

- (g) Error recovery.

- (h) Sequencing.

- (i) Congestion control and user data flow control.

- (j) Restart.

The ISU central office is designed to support all specified standards except 2B1Q at the U-Interface. The initial design uses a pseudo U-Interface, as the project was started prior to the acceptance of the standard. At a later date, LAP-D and Q.931 is to be implemented in software as another Master of Science thesis project.

# CHAPTER 3. THE ORIGINAL CENTRAL OFFICE DESIGN

Geetha Venkataraman, a Computer Engineering Master of Science graduate in 1990, completed a partial design and hardware implementation of the original central office as part of her graduation requirements. Her thesis was based upon that partial design.

Availability of accurate and detailed information on the original ISU central office design from the designer was sparse. The thesis was difficult to follow, and only inaccurate hand sketched schematics were available. Consequently the major sources of information used to evaluate the design were the MITEL "Microelectronics Data Book", the hardware implementation circuitry, parts of her thesis, Dr. Douglas W. Jacobson, her major professor, and Angela Bradley, a Computer Engineering graduate student assigned to the design of the S/T-Interface.

#### Goals

The principle design goals of the original ISDN central office project at ISU were:

- 1. To implement current CCITT ISDN local exchange standards (e.g. central office) in an IBM XT PC providing:

- (a) Layer 1 and partial Layer 2 functions in readily available hardware;

- (b) a primary rate interface for the user;

- (c) a basic rate U-Interface for the user;

- (d) a basic rate S/T-Interface for the user;

- (e) routing from user to user via a digital switch;

- (f) and timing signal generation as required.

- 2. Software running on the IBM XT PC, providing the following functions:

- (a) implementation of the X.25 and Q.931 protocols;

- (b) and perform all routing through the digital switch,

- 3. The user physical access through special ISDN telephone jacks.

- 4. Minimal complexity in the implementation of the central office design.

#### The PC Card

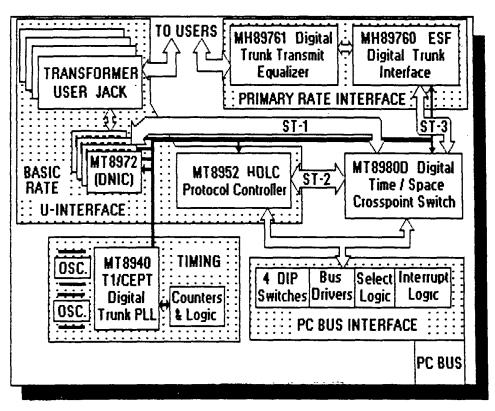

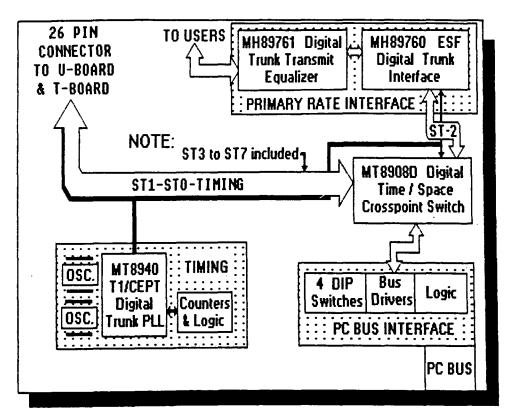

A partial design was implemented on a single PC board, as illustrated in Figure 3.1, using MITEL's ST-BUS family of ISDN system components. The hardware design consisted of six distinct functional groupings, namely:

- 1. The ST serial bus, with a bandwidth capacity meeting basic rate, North American primary rate, and European primary rate requirements.

- 2. The PC bus interface, consisting primarily of bus drivers.

- 3. Timing circuitry to provide the timing required on the ST bus.

- 4. U-Interface MITEL ISDN chips and supporting circuitry consisting of:

Figure 3.1: The Original ISU Central Office Hardware Design

- (a) four Digital Network Interface Chips (DNICs);

- (b) four 2:1 transformers with capacitors and resistors, providing the user a physical interface to the line pins on the DNICs;

- (c) an HDLC Protocol controller, providing X.25 level-2 functions, data buffering, and address recognition for routing.

- 5. Primary rate interface to a T1 line using a Digital Trunk Interface chip and a Digital Trunk Transmit Equalizer.

- 6. A Digital Crosspoint Switch providing routing over 16 ST busses which consist of 256 incoming channels and 256 outgoing channels.

### The MITEL ST-BUS

Figure 3.2: The ST-BUS BRI Channels and Timing

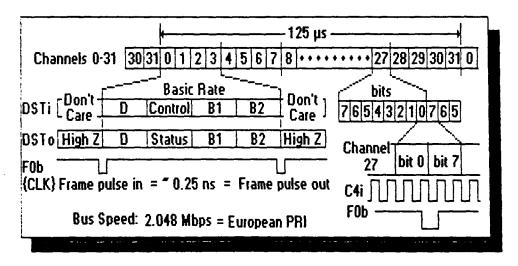

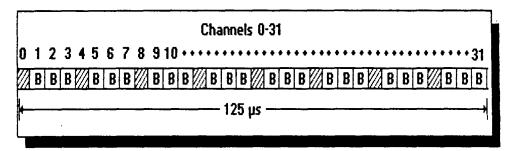

Complying with the ISDN standards and PCM requirements of eight thousand voice samplings per second, the ST-BUS is based upon the overall time frame of 125

microseconds, as depicted in Figure 3.2. The ST-BUS is serial and uni- directional, and therefore two busses are required for full duplex transmission capabilities as required in ISDN. Each bus is time divided into 32 channels, which are subdivided into 8 bit segments within each sampling period.

There are two types of busses defined, data and control, each requiring two directional busses: input, from the user to the network; and output, from the network to the user. The control buses were not used in this design. Data bus pins and busses are denoted as DSTi or Di for input and DSTo or Do for output. When used at the Basic Rate Interface, each bus can support multiplexing of up to eight interfaces, which in turn support multiplexing of TEs over the B and D channels [19].

As illustrated in Figure 3.2, each BRI device is alotted four channels, the B and D channels plus a STi control channel or a STo status channel. The control and status channels are used to communicate with the interface chips, especially at the U-Interface. Due to the different interfaces supported (BRI and PRI), the time subdivision of the busses, and the multiplexing ability of the bus, several clock speeds are required for synchronization.

### ST-BUS Timing Generation

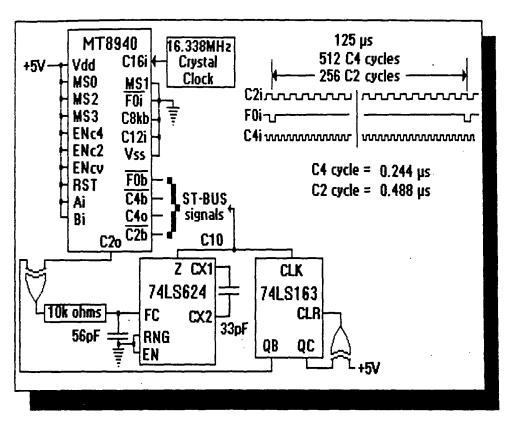

ST-BUS Waveforms The primary chip used to generate timing for the ST-BUS system is the MT8940. In the original central office design, four signals were required, as depicted in Figure 3.3. The MT89760 Digital Trunk Interface required the  $\overline{C2i}$  and the  $\overline{F0i}$  framing pulse. The  $\overline{C2i}$  synchronizes bit transmission, just as the  $\overline{C4i}$  signal in all the other MITEL circuits used in the design. All circuits require the frame pulse to synchronize the four channel segments on the ST-BUS.

Figure 3.3: The ST-BUS Clock Signal Generation Diagram

The C10 signal, produced by the synchronous timing generation circuit, is used by the MT8972B DNICs at pin number 16. The synchronous timing generation circuit is composed of two exclusive-or gates, two capacitors, one resistor, a 4-bit synchronous counter, 74LS163, and a voltage controlled oscillator, 74LS624.

# The PC Bus Interface

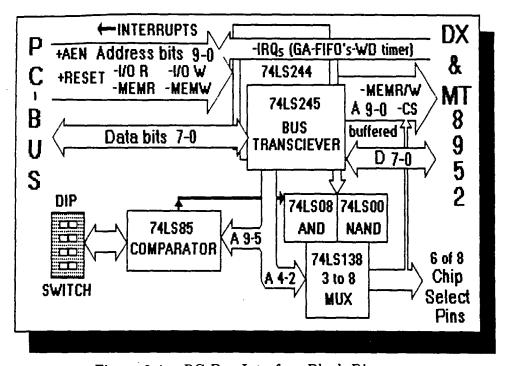

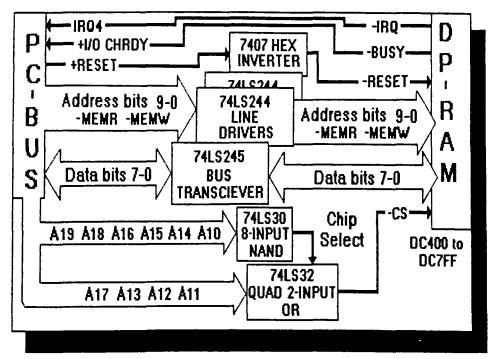

Figure 3.4: PC-Bus Interface Block Diagram

The PC bus interface on the card on which the original central office was built was prewired via printed circuits. It consisted of the devices diagrammed in Figure 3.4, and offered 10 buffered address lines 8 buffered data lines, buffered I/O Read and Write, reset, 8 chip selects, and interrupt logic.

# The Primary Rate Interface

The PRI was incomplete due to a missing trunk line interface chip. Therefore since it is inactive, little detail on the PRI of the design is included. The primary piece of hardware in the design of the PRI is the MT89760, ESF Digital Trunk Interface, which possesses the following features [19]:

- With a T1 Digital Trunk Transmit Equalizer, MT89761, a complete interface to a bidirectional T1 link.

- D3/D4 or ESF framing and SLC96 compatible.

- Two frame elastic buffer with 32 microsecond jitter buffer.

- Insertion and detection of A, B, C, and D status bits.

- Signaling freeze and optional debounce.

- Robbed bit signaling, overall or per channel.

- Frame and superframe synchronization signals.

- AMI encoding and decoding.

- Overall, per channel, and remote loop around.

- Eight kiloHertz synchronization output.

- Digital phase detector between T1 and ST-BUS.

- Bipolar violation count, frame error count, and CRC error detection.

Figure 3.5: ST-BUS Channels at the PRI

The MT89760 interfaces directly to a Digital Crosspoint Switch via the ST-BUS. The channel allocation on the ST-BUS for the PRI differs from the channel allocation for the BRI, as illustrated in Figure 3.5, above. Additional timing signals are also required for digital ST-BUS bit insertion and T1 line synchronization, as illustrated in Figure 3.5. Function control and status can be monitored through registers, via a serial control ST-BUS at the switch by the PC. Timing is provided by the MT8940, as previously depicted in Figure 3.5.

### The MT8980D Digital Crosspoint Switch

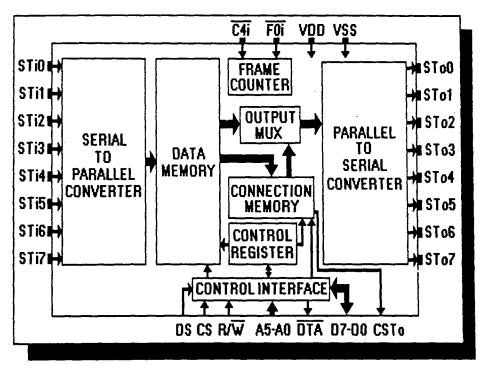

DX's Features and Functions The MT8980D, DX, is the key device in the original design. All communication on the serial busses must pass through it, and a communication path exists to the PC. The primary functions and features of the DX are [19]:

- MITEL ST-BUS compatible, with 8 line by 32 channel inputs and 8 line by 32 channel outputs forming a 256 port non blocking switch.

- Low power consumption (30mW) and +5 Volt single power supply.

- Microprocessor-control interface, provides access to individual channels.

Figure 3.6: The MT8980D Functional Block Diagram

• Three-state capabilities on all eight serial outputs.

The MT8980D and MT8981D are the two digital switches offered by MITEL. The MT8981D supports four input ST busses and four output ST busses. The MT8980D supports eight busses of each, as illustrated in Figure 3.6, resulting in a switching capacity of 256 channels input by 256 channels output. For this design the MT8981D would be sufficient, but for expandability the MT8980D was chosen. The MT8980D is cascaded in designs requiring more than 256 channels.

Memory Description The MT8980 contains two distinct memories, the data memory and the connection memory. The data memory consists of 256 eight bit words, corresponding to the 256 eight bit incoming channels. The connection memory also consists of 256 locations, corresponding to the 256 eight bit outgoing channels, with each location consisting of low and high parts of eight bits each. The high order bits are channel control bits, while the low order bits designate the address of the input channel's data stored in data memory, as illustrated in Table 3.1.

Access by the PC or microprocessor is accomplished directly via normal data, control, and address bus to memory interface connections. The data memory is a read only memory, while the connection memory is a random access memory and is accessible only through the control register.

The Control Register Data in the Control Register consists of mode control, memory select, and stream address bits, as depicted in Table 3.2. Bit 7 allows split memory operations as indicated. Message mode allows the PC or microprocessor to write or broadcast to all channels on all output busses simultaneously, via each

Table 3.1: MT8980D Connection Memory Bits

| BIT        | NAME      | DESCRIPTION                                             |

|------------|-----------|---------------------------------------------------------|

|            |           | HIGH PART                                               |

| 7-3        | Unused    | read as logical '0's                                    |

| 2          | Message   | When '0' low order bits address data memory             |

| [ [<br>] ] | Channel   | When '1' the low order bits are outputted               |

| 1          | CSTo bit  | Value of this bit to CSTo pin one channel early         |

| 0          | Output    | When ODE pin is high and Control Register bit 6 is '0', |

| <u> </u>   | Enable    | the output driver is enabled thereby allowing           |

|            |           | the construction of switching matrices                  |

|            |           | LOW PART                                                |

| 7-5        | Bus Addr. | Address the incoming bus 0-8 ('100' is STi4)            |

| 4-0        | Channel   | Address the incoming channel 0-31                       |

|            | Address   | bit 4 is the most significant bit                       |

Table 3.2: MT8980D Control Register Bits

| BIT | NAME    | DESCRIPTION                                             |

|-----|---------|---------------------------------------------------------|

| 7   | Split   | '1' reads from data and writes to low connection memory |

|     | Memory  | '0' memory select bits determine subsequent operations  |

| 6   | Message | '1' & ODE pin '1', low connection memory is put on bus  |

|     | Mode    | '0' connection memory bits determine channel output     |

| 5   | Unused  |                                                         |

| 4-3 | Memory  | '00' Not to be used                                     |

|     | Select  | '01' Data memory is read only                           |

| Įį. | Bits    | '10' Connection memory - low part                       |

|     |         | '11' Connection memory - high part                      |

| 2-0 | Stream  | The binary number expressed refers to the input         |

|     | Address | or output ST-BUS stream corresponding to the subsection |

|     | Bits    | of memory made accessible for subsequent operations     |

connection memory location's low order bits. Otherwise when bit 6 is 0, the high order connection word dictates output.

The memory select bits designate which of the three memories can be read from or written to. Stream address bits together with the pins A4-0, determine the address of the memory location being accessed. A5 asserted low provides access to the Control Register, which can be read from as well as written to.

The control bits must be changed prior to changing reading or writing modes. The ODE pin, when low, can cause all outputs to go to high-impedance, therefore it is wired high. High-impedance is therefore achieved only via software control.

Functional Description Serial data is received at each of the eight bus inputs, converted to eight bit parallel words and stored in the 8x256 data memory, which can be read by the PC or microprocessor to ascertain destination addresses for switch routing. Switching is accomplished by writing to the low connection memory locations, after control register setup. Any input channel can be switched to any output channel. All ST-BUS frame and bit timing is derived from the  $\overline{F0i}$  and  $\overline{C4i}$  pins.

### The U-Interface Components

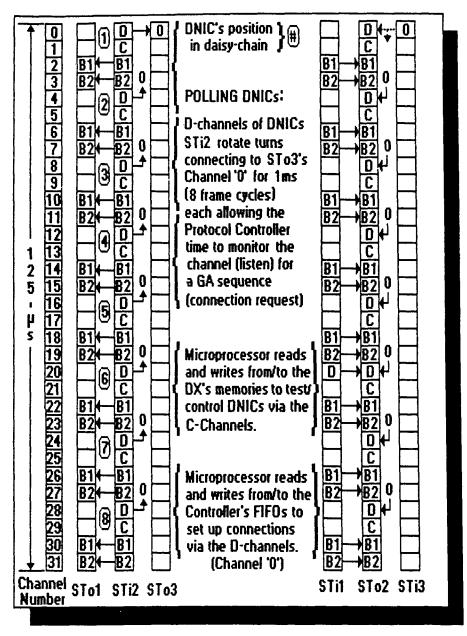

The DX pulled double duty, because it aided in implementing the U-Interface. It allowed the PC access to the DNICs' control registers via the C-channels. One set of busses (e.g. input and output) connected the switch to a group of 4 daisy-chained MT8972B Digital Network Interface Circuits, while a second set of busses connected to a MT8952 HDLC Protocol Controller, which performed X.25, Level-2 functions.

Figure 3.7: C-Channel DNIC Control Routing

The DX switched the incoming C-channels from the DNIC bus to the outgoing bus of the Protocol Controller, establishing a control path to the DNICs. The DX could also communicate directly with the DNICs via low connection memory and data memory, as in Figure 3.7. Each DNIC's B channel was also switched to channel 0 going to the Controller in a predefined order. The Controller monitored the channel and when a GA sequence was detected sent an interrupt to the PC.

# MITEL's MT8972B Digital Network Interface Circuit

DNIC Features and Functions The MT8972B, DNIC, was designed primarily as a U-Interface device for ISDN, but may be used in other applications such as a high speed, short distance modem. Some of the DNIC's functions and features allowing such diversity are [19]:

- Full duplex transmission over a single twisted pair.

- Selectable 80 kbps or 160 kbps line rate.

- Adaptive echo cancellation.

- Maximum line range of 4 km at 160 kbps or 5 km at 80 kbps.

- ISDN compatible 2B+D data format.

- Transparent modem compatibility.

- ST-BUS compatible.

- Low power consumption of 50mW.

- Single 5 Volt power supply.

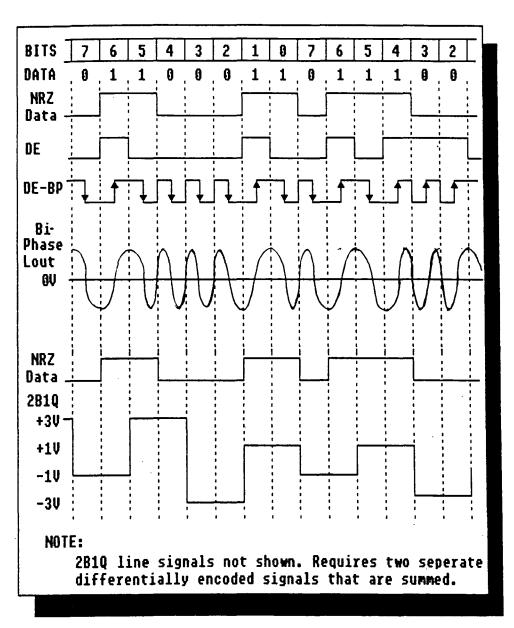

Additional functional flexibility is provided within the ISDN environment, and consequently the DNIC offers several modes of operation, which are illustrated in Table 3.3. The DNIC converts line signals to ST-BUS format, and vice versa, to provide a common interface for networking to other ISDN components. Full duplex interface to the user is accomplished via a 2:1 transformer and a twisted pair. Line signaling was implemented using biphase signaling instead of 2B1Q as defined in ISDN U-reference point standards.

Table 3.3: MT8972B Mode Definitions

| MODE  | FUNCTION                                                           |

|-------|--------------------------------------------------------------------|

| SLV   | SLAVE: timing extracted from line data and is output to the system |

| MAS   | MASTER: timing supplied by system clocks (ST-BUS timing)           |

| DUAL  | DUAL PORT: Control and D channel are active on one bus,            |

|       | B channels are active on another                                   |

| SINGL | SINGLE PORT: Control, B and D channels are active on same bus      |

| MOD   | MODEM: non formatted line data is handled by the DV port           |

|       | at 80 or 160 kbps                                                  |

| DN    | DIGITAL NETWORK: data configured according to ISDN standards       |

| D-C   | D BEFORE C-CHANNEL: D-channel is transmitted before C-channel      |

| C-D   | C BEFORE D-CHANNEL: C-channel is transmitted before D-channel      |

| ODE   | OUTPUT DATA ENABLE: high impedance during power up                 |

Modes of Operation Mode 0 was chosen in order to daisy-chain DNIC's, providing multiple interfaces with a minimal amount of supporting hardware. It provides DN, ODE, SINGL, MAS, and D-C operating modes. In DN (Digital Network) mode the line carries the ISDN data format, including a housekeeping bit on the control (C) channel. Single port mode allows access to the control, B and D channels on the same ST-BUS, as in Figure 3.2. ODE allows serial port outputs to be tristated to prevent damage on power up. MAS (Master) mode allows the DNIC to operate

via external ST-BUS timing.

Biphase Line Signaling The DNIC deviates from the latest adopted CCITT U-Interface signaling standard, 2B1Q, by using biphase line signaling, shown in Figure 3.8. A 2B1Q coding example was described in Chapter 2. When the DNIC was designed, 2B1Q was still being researched. Biphase signaling was a proven, cost effective technique that was readily available on the market. Performance is the primary advantage of 2B1Q, expanding the effective distance of transmission by over 25%. Cost, two twisted pair lines instead of one as in biphase signaling, and signal recovery complexity are the primary disadvantages.

2B1Q requires six to eight times more bit history to cancel out signal echo than does biphase signaling. The primary reason for this is that 2B1Q produces a bandwidth four times narrower than biphase. This reduces noise interference, but since pulses output on the line tend to develop long tails, it also leads to intersymbol interference between consecutive pulses. Cleaning up this interference leads to the more complex circuitry required for 2B1Q.

Table 3.4: MT8972B Status Register

| BIT | NAME   | FUNCTION                                                 |

|-----|--------|----------------------------------------------------------|

| 0   | SYNC   | Synchronization: when '1' indicates Lin sync is acquired |

| 1-2 | CHQual | Channel Quality: the farther from 0 the better the SNR   |

| 3   | Rx HK  | This is the received housekeeping from the other end     |

| 4-7 | DNIB   | Reserved for future functionality                        |

Internal Registers The C-channel is used for communication between the DNIC and the system. This is accomplished by writing to and receiving from the

Figure 3.8: Line Signaling Waveforms

DNIC's internal registers. The DNIC contains three registers defined as follows:

- the control register, is a write only register whose functions are detailed in Table 3.5;

- the diagnostic register, is a write only register whose functions are detailed in Table 3.6;

- and the status register, is a read only register whose functions are detailed in Table 3.4;

Table 3.5: MT8972B Control Register

| BIT | NAME    | DESCRIPTION                                                |

|-----|---------|------------------------------------------------------------|

| 0-1 | Reg Sel | Register select: must be '00' to select control register   |

| 2   | Future  | must be set to '0'                                         |

| 3   | BRS     | Bit Rate Select: '0' is 80 kbps, '1' is 160kbps            |

| 4   | DNIB    | D-channel in B slot: active when '1'                       |

| 5   | PSEN    | Prescrambler/Deprescrambler Enable: active when '1'        |

| 6   | ATTACK  | Set to '1' on power up for fast echo canceller convergence |

| 7   | TxHK    | Transmit housekeeping bit: '1' active, '0' inactive        |

The Control Register is used to establish bit rates when used as a modem, control the transmission of the housekeeping bit on the Lout line, and control some onboard functions. All of the registers are accessed via the C-Channel through the Protocol Controller by the PC.

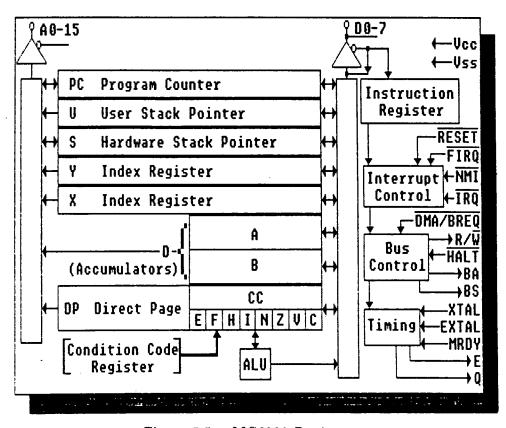

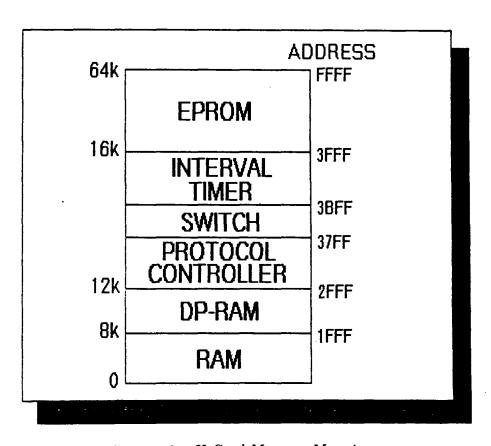

The Diagnostic Register is used for testing of the lines, the ST-BUS, and the DNIC's internal functions. Testing is performed both at power up and during normal operations via the housekeeping bit. Results of some of the testing procedures are stored in the Status Register, which also monitors channel quality. Other results are